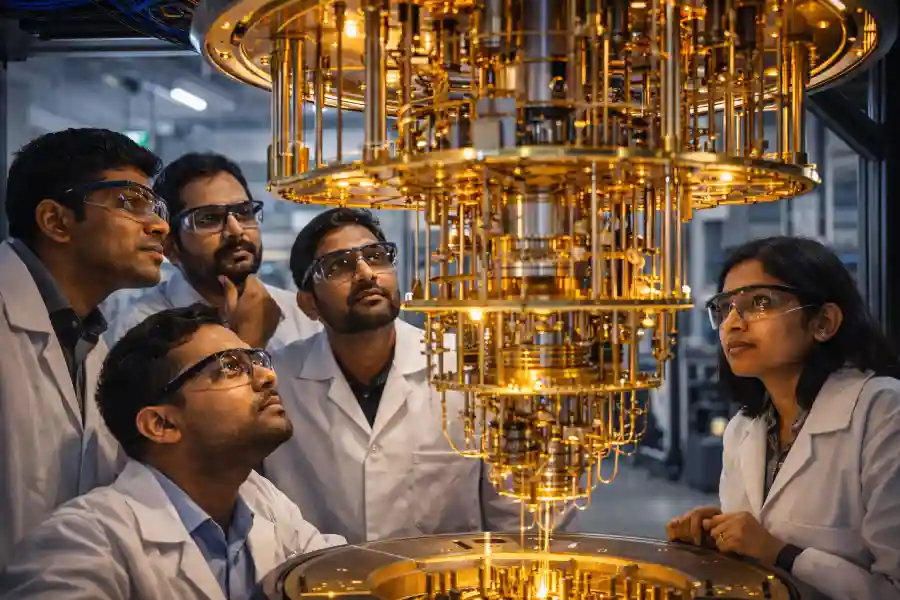

With Kaveri, QpiAI scales up from its 25-qubit Indus system to a 64-qubit superconducting processor built in India.

Bengaluru-based QpiAI has introduced Kaveri, a 64-qubit superconducting quantum processor developed in India. The chip follows the company’s earlier system, Indus, which operated with 25 qubits under the National Quantum Mission. Indus marked QpiAI’s entry into quantum hardware. Kaveri increases the qubit count and reflects continued work on superconducting architecture.

The company describes the processor as part of its in-house quantum platform rather than a standalone prototype. With successive hardware releases, QpiAI is extending its own development cycle instead of relying on imported quantum systems.

Inside Kaveri’s Hardware

Kaveri uses superconducting transmon qubits. To function, the processor is kept at extremely low temperatures inside specialised cooling equipment known as dilution refrigerators. Public descriptions of the processor note that it runs at temperatures colder than deep space, a common reference point for superconducting systems that require extreme cooling to function. The chip has been built using wafer-scale fabrication techniques along with flip-chip integrated technology designed to reduce signal loss.

QpiAI also references low-loss interconnect layers and a separation between qubit and control circuitry to improve performance stability. The system is structured as a 64-qubit device within the Noisy Intermediate-Scale Quantum (NISQ) category, meaning it is suited for experimental and algorithm development rather than large-scale fault-tolerant computing at this stage.

According to QpiAI’s technical roadmap, Kaveri targets coherence times of approximately 100 microseconds and error rates around 10⁻², which are typical benchmarks for superconducting systems in this generation. The qubits are laid out in a grid. Additional integration layers are used to improve how they communicate with one another.

Surface code error correction techniques are referenced as part of the architecture roadmap, although full fault tolerance remains a longer-term goal. The system integrates into QpiAI’s hybrid quantum-classical framework, combining quantum processing with conventional high-performance computing resources. This hybrid structure reflects how most current quantum systems are deployed globally, where classical processors handle optimisation loops while quantum hardware executes specific subroutines.

Future Processors and Research Engagement

The company also has a number of future processors lined up after Kaveri, like the Ganges, targeting 128 qubits, and Everest, projected at 1000 qubits. These systems are part of its stated plan to scale qubit counts gradually while improving stability and control precision. While core design and validation are being handled within India, certain specialised components continue to rely on international supply chains.

The company has not indicated a fixed commercial timeline for the higher-qubit systems, but the roadmap suggests incremental scaling rather than a single leap in architecture.

QpiAI has tied its quantum hardware work to academic engagement through its QVidya initiative and a link with Alliance University. The association connects university programmes with the company’s quantum systems. Faculty and students are being introduced to practical aspects of quantum computing, including hardware environments and algorithm development. Access to tools related to the Kaveri processor is part of this engagement. The company has said that the chip will primarily be used in research contexts for optimisation problems, simulation exercises, and experimental computing tasks.

Commercial deployment timelines have not been detailed. For now, the processor is being described as a platform for testing and applied study rather than large-scale commercial use.

Funding and Ongoing Development

QpiAI has reported raising approximately $32 million in funding to support its ongoing quantum hardware work. The Kaveri processor was introduced at a science and technology event in Delhi attended by government representatives and industry participants. The launch formed part of broader discussions around domestic quantum research and hardware capability.

The 64-qubit system follows the company’s earlier Indus processor and represents its second superconducting chip platform. Development work continues as the company refines system stability and control precision. QpiAI has also listed additional processors under the names Ganges and Everest, which are intended to carry higher qubit counts in later phases. These systems remain under development as part of the company’s stated hardware plans.

In case you missed:

- Schrödinger’s Cat Just Made Quantum Computers 160x More Reliable!

- Japan just made Remote Quantum Computing a reality!

- Humans Just Achieved Teleportation? Clickbait vs. Facts

- Tata Electronics to Manufacture Intel Chips & AI Laptops in India!

- Goodbye Blackwell, Hello Rubin: Nvidia’s new AI platform is here!

- Quantum Computers: It’s now 20X easier to crack Bitcoin encryption than we thought!

- India’s first Aatmanirbhar semiconductor chip is finally here!

- Quantum War Tech: DRDO and IIT help India take the lead!

- Aatmanirbhar Push: India Becomes 7th Nation to Crack Gallium Nitride Chip Technology

- India’s First Paid Chip Prototype: Kaynes Fires the Starting Shot